远程调试C++程序 - 配置vscode的launch.json和tasks.json

参考vscode 官方文档

插件安装列表

C/C++

C/C++ Extension Pack

Clang-Format

CMake

CMake Tools

Remote - SSH

Remote - SSH: Editing Configuration Files

Remote Explorer

编辑代码

远程编辑

参考:vscode环境搭建 - SSH、Google Test 和 CMake

格式化代码

找到Clang-Format插件设置,将其中如下选项设置为Google:

Clang-format: Fallback Style

Clang-format › Language › C: Style

Clang-format › Language › Cpp: Style

Clang-format: Style

在设置中搜索Format On Save,打上勾

构建工程

CMake

点击 vscode 底部状态栏,选择编译器

选择一个比较新版本的编译器

之后 CMake 会自动运行

点击下面的[all]可以选择生成项目中某个可执行文件,默认生成所有;点击生成可以开始 ...

EDA流程学习 - 设计规则检查(DRC)

参考:《Electronic Design Automation for IC Implementation, Circuit Design, and Process Technology》Chapter 20

INTRODUCTION

制造设计:(Design for Manufacturability, DFM),是一种方法和技术,旨在确保设计能够在制造过程中高效、可靠地生产出来。

模式匹配:(Pattern Matching, PM),是一种验证设计规则的方法。

多段光刻技术:(Multi-Patterning Technology, MPT),是一种用于曝光光刻的技术。

CONCEPTS

验证时,几何图形被分组到层中:

Drawn layers 表示原始布局数据,输入验证系统时图形会被合并,消除几何重叠或相邻。

Polygon layers 作为层创建操作(如布尔运算、拓扑多边形操作或几何测量函数)的输出。

Edge layers 表示合并多边形的边缘,按长度、角度或其他属性分类。

Error layers 包含 DRC 空间测量的一个到四个边缘的聚类,用于图形结果表示。 ...

数学符号及其对应的LaTeX代码

由于之前写学习笔记时总是不会输入数学符号,这时候就跑到搜索引擎里面去搜索,再复制。索性自己抄写一遍,后续再需要复制可以来这里。

参考 Art of Problem Solving

Operators

Symbol

Command

Symbol

Command

Symbol

Command

±\pm±

\pm

∓\mp∓

\mp

×\times×

\times

÷\div÷

\div

⋅\cdot⋅

\cdot

∗\ast∗

\ast

⋆\star⋆

\star

†\dagger†

\dagger

‡\ddagger‡

\ddagger

⨿\amalg⨿

\amalg

∩\cap∩

\cap

∪\cup∪

\cup

⊎\uplus⊎

\uplus

⊓\sqcap⊓

\sqcap

⊔\sqcup⊔

\sqcup

∨\vee∨

\vee

∧\wedge∧

\wedge

⊕\oplus⊕

\oplus

⊖\ominus⊖

\ominus

⊗\otimes⊗

\otimes

∘\circ∘

\circ

∙\bullet∙

\bullet

⋄\diamon ...

《集成电路静态时序分析与建模》学习笔记

第一章 - 引论

静态时序分析

静态时序分析(static timing analysis, STA)是分析、调试并确认一个门级系统设计时序性能的比较彻底的方法。静态时序分析既要检验门级电路的最大延迟、以保证电路在指定的频率下能够满足建立时间的要求,同时又要检验门级电路的最小延迟、以满足保持时间的要求。

静态时序分析的优点:

静态时序分析执行速度快

静态时序分析不需要测试向量

静态时序分析对于有时序路径的时序,测试覆盖率可以近乎达到 100%

静态时序分析能够完成动态仿真所不能实现的复杂分析

静态时序分析的缺点:

静态时序分析不能验证设计的功能

静态时序分析只能验证同步时序电路的时序特性

静态时序分析不能自动识别设计中的特殊路径

第二章 - 静态时序分析的基础知识

信号线延时的定义为:逻辑信号从逻辑门单元的输出端口考试在互连线上传播到下一级逻辑输入端口的延时。

建立时间和保持时间

恢复时间和移除时间

时序单元的时序分析必须满足输入信号脉宽大于最小脉冲宽度的要求,否则时序分析结果就可能与实际情况不一致,主要原因之一就是无法保证时序单元实现正常的逻辑功能。

时序路径

触发器到 ...

EDA后端总体概览

在粗略阅读《数字集成电路物理设计》这本书之后,与其说花费很多时间精力去研读其中的细节,倒不如先进行一次复习,将自己所理解的 EDA 物理设计的流程以及关键技术总结成图。

各部分组成

物理设计

状态图

活动图

《数字集成电路物理设计》学习笔记

缩写:

电子设计自动化:EDA, electronic design automation

技术节点:technology node

极紫外:EUV, extreme UV, 波长 13nm

逻辑综合:logic synthesis

分配:partition

模块化:module

自底向上的堆砌法:buttom-up

自上向下:top-down

指令窗:CIW, command in window

点工具:point tools

图形界面:GUI, griphic user interface

设计流程:flows

设计平台:platforms

片上系统芯片:SoC, system-on-chip

设计公司:fabless

晶圆代工厂:foundry

设计生产链:design chain

深亚微米:DSM, deep sub-micron

时序驱动设计:TDD, timing-driven design

天线效应:PAE, process antenna effect

信号完整性:SI, signal integrity

光学近似检查:OPC, optical proximity c ...

《超大规模集成电路物理设计:从图分割到时序收敛》学习笔记

第一章 - 绪论

电子设计自动化(EDA)

VLSI 设计流程

各个步骤做的事情:

系统规范:定义系统的总体目标和高级需求,包括功能、性能、物理尺寸和生产技术。

架构设计:在满足系统规范的情况下选择各种实现。

功能和逻辑设计:使用硬件描述语言(HDL)定义芯片的功能和时序行为。使用逻辑综合工具将 HDL 与工艺库结合起来。

电路设计:一些关键的低端的单元必须在晶体管级来进行设计。包括静态 RAM 模块、I/O、模拟电路、高速函数(乘法器)以及静电放电(ESD)保护电路。电路级仿真工具可以验证电路级设计的正确性。

物理设计:布局、布线。物理设计影响电路性能、面积、可靠性、工具和制造产量。

划分:将电路分解成功效的子电路或者模块,使之能够单独设计或者分析。

布图规划:决定子电路或者模块的形状和布置,以及外部端口、IP 或者宏模块的位置。

电源和地网布线:经常在布图规划中,分布电源(VDD)和地(GND)线网在芯片各处。

布局:确定在每个模块中的所有单元的空间位置。

时钟网综合:决定了时钟信号的缓冲、门控(例如电源管理)和布线,以满足规定的偏移和延迟需求。

总体布线:分配布线资源用于连 ...

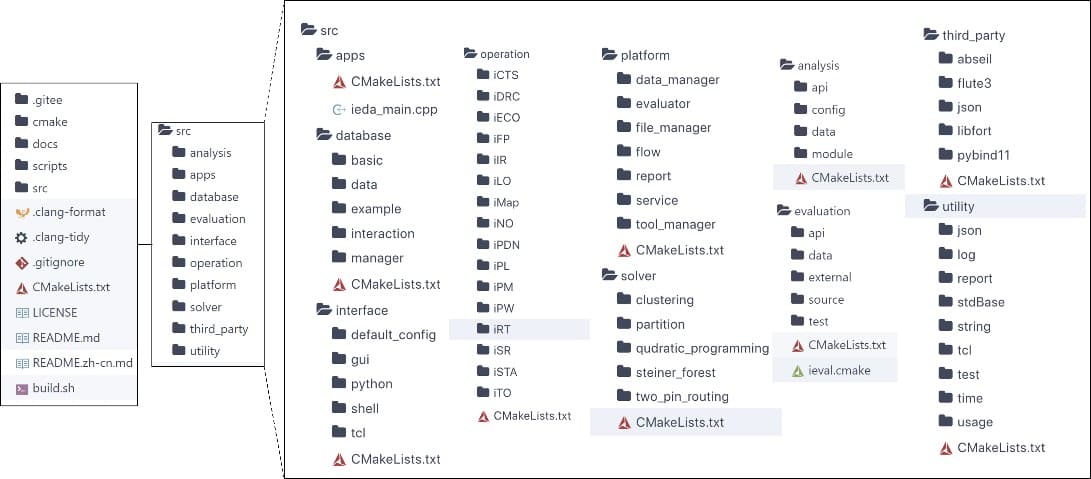

开源EDA软件iEDA初探 - 基本架构及代码框架

系列文章

-> 开源EDA软件iEDA初探 - 基本架构及代码框架

开源EDA软件iEDA源码解析 - iDRC

上大学的时候,教集成电路的老师就跟我们讲:“中国的芯片制造,除了光刻机,另一个被卡脖子的技术就是 EDA 软件。”

这个课的课程设计,按照以往来说是老师布置一些题目,使用 EDA 软件绘制一个运算放大器,或者一个电源模块的版图之类的。

但老师手上正好有一个项目,是一个微能源的项目,使用 MEMS 工艺在晶圆上制作出微小悬臂,然后在悬壁上覆盖好压电陶瓷,这样当芯片受到微小震动时压电陶瓷上就会产生微弱的电荷。我们的任务就是在芯片上制作出一个电荷收集和存储的模块,将这个微弱的能量累积起来。当到达一定程度之后,让射频模块发射一次信号,就可以让一个传感器在自供电的情况下运行数年之久。

这便是我跟 EDA 软件最初的渊源,为现在的学习,以及接下来将要进入到的工作埋下了伏笔。

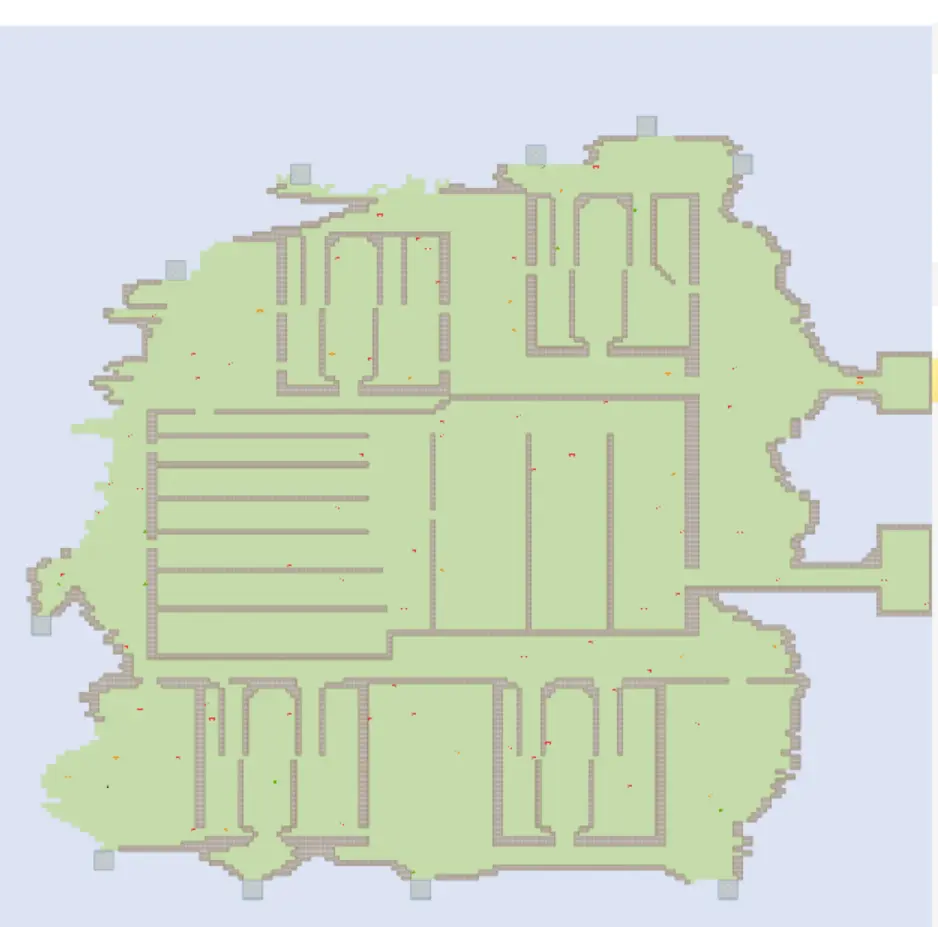

当时画的,非常不专业的版图:

iEDA

TODO 介绍

我总结出来的架构图

我所理解的目录说明

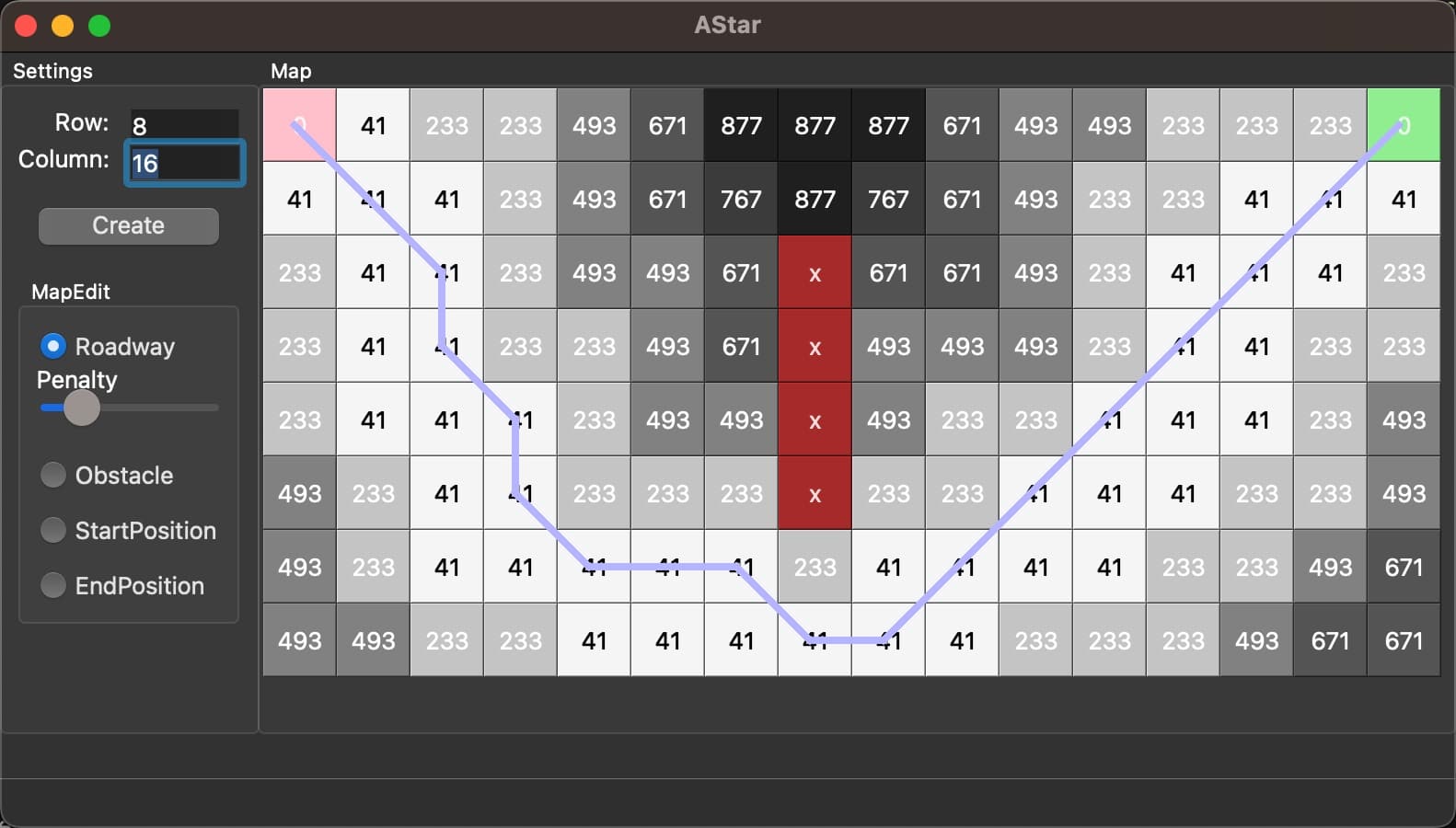

A*算法深入探究 - 使用Qt和C++实现带权重版本的A*

系列文章

A算法初探究及优化 - 自动解贪吃蛇

-> A算法深入探究 - 使用Qt和C++实现带权重版本的A*

A算法扩展 - 三维A

已知如下图地图,黑色表示障碍物无法通行,要求实现避障算法寻找从红色起点出发达到绿色终点的最优路径。

要求:

对图中的地图进行建模,抽象成类,对数据进行封装;

思考寻路算法的实现,对问题进行拆解,对算法实现也要求抽象接口类;

使用给定的 C++ 工程模板,按照模板编写 CMakeLists.txt,以及 Google Test 单元测试,DoxyGen 注释的使用。

工程模板

兴权老师给了一个思考题:如果不是两个点,是三个点甚至更多的点,需要寻找一条最短路径连起来,应该怎么做?(调研发现有一个算法:斯坦纳树)

问题分析

由题可以得出的信息

题图中给出的并非最优路径。

想到 A* 算法,之前研究该算法的文章:A*算法初探究及优化 - 自动解贪吃蛇

可以进行斜向移动,所以每个结点的邻居有 8 个

使用一定的方法展示出所寻得的路径

想要达到的目标

将地图抽象成类,将 A* 算法抽象成类

A* 算法依赖地图类,但地图类不应回头依赖 A ...

《Effective Modern C++》学习笔记

现代 C++(即 C++11/C++14)远不止是修修补补。考虑所有的功能,这简直是一门语言的脱胎换骨。

绪论

一个对象是右值意味着能够对其实施移动语义,而左值则一般不然。

有一种甄别表达式是否左值的实用方法富有启发性,那就是检查能否取得该表达式的地址。如果可以取得,那么该表达式基本上可以断定是左值。如果不可以,则其通常是右值。

第一章 - 型别推导

条款 1:理解模板型别推导

在模板型别推导过程中,具有引用型别的实参会被当成非引用型别来处理。换言之,其引用型会被忽略。

对万能引用形参进行推导时,左值实参会进行特殊处理。

对按值传递的形参进行推导时,若实惨型别中带有const或volatile饰词,则它们还是虎背当作不带const或volatile饰词的型别来处理。

在模板型别推导过程中,数组或函数型别的实参会退化成对应的指针,除非它们被用来初始化引用。

条款 2:理解 auto 型别推导

12auto x3 = { 27 };auto x4{ 27 };

以上两条语句,auto 推导出来的型别为std::initializer_list ...